## 4A, 2MHZ HIGH PERFORMANCE SYNCHRONOUS BUCK CONVERTER

## Description

The AP3440 is a current mode, PWM synchronous buck (step-down) DC-DC converter, capable of driving a 4A load with high efficiency, excellent line and load regulation.

The device integrates two N-channel power MOSFETs with low onresistance. Current mode control provides fast transient response and cycle-by-cycle current limit.

The switching frequency of AP3440 can be programmable from 200kHz to 2MHz, which allows small-sized components, such as capacitors and inductors. A standard series of inductors from several different manufacturers are available. This feature greatly simplifies the design of switch-mode power supplies.

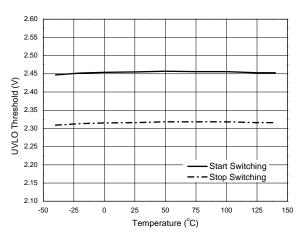

Under voltage lockout is internally set at 2.6V, but can be increased by programming the threshold with a resistor network on the enable pin. The output voltage startup ramp is controlled by the soft-start pin. An open drain power good signal indicates the output is within 93% to 107% of its nominal voltage.

The AP3440 is available in U-QFN3030-16 package.

## Applications

- Low-voltage, High-density Power Systems

- Point of Load Regulation for High Performance DSPs, FPGAs, ASICs and Microprocessors

- Broadband, Networking and Optical Communications

Infrastructure

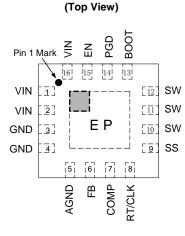

## **Pin Assignments**

#### U-QFN3030-16

### Features

- Input Voltage Range: 2.95V to 5.5V

- 0.8V Reference Voltage with ±3% Precision

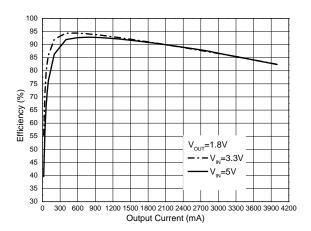

- Two 30mΩ (Typical) MOSFETs for High Efficiency at 4A Load

- High Efficiency: Up to 94%

- Output Current: 4A

- Programmable Frequency:200kHz to 2MHz

- Current Mode Control

- Synchronizes to External Clock

- Adjustable Soft-start

- Soft Start-up into Pre-biased Output

- UV and OV Power Good Output

- Built-in Over Current Protection

- Built-in Thermal Shutdown Function

- Programmable UVLO Function

- Built-in Over Voltage Protection

- Thermally Enhanced 3mm×3mm 16-pin U-QFN3030-16

- Totally Lead-free & Fully RoHS Compliant (Note1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- 2. See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

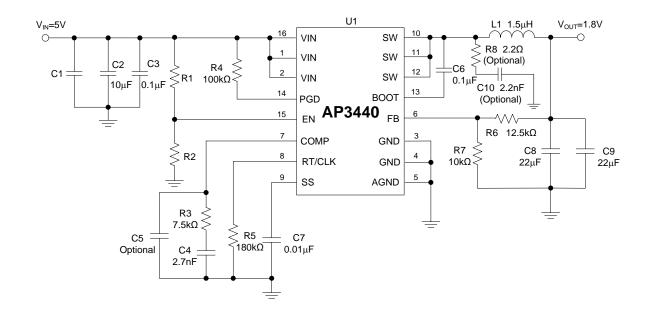

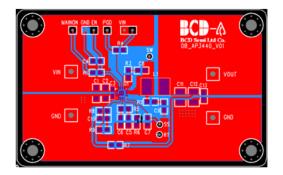

## **Typical Applications Circuit**

## **Pin Description**

| Pin Number | Pin Name            | Function                                                                                                                                                                                                   |  |

|------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1,2,16     | VIN                 | Supply input pin. A capacitor should be connected between the VIN and GND pin to keep the DC input voltage constant                                                                                        |  |

| 3,4        | GND                 | Power ground. This pin should be electrically connected to the power pad under the IC                                                                                                                      |  |

| 5          | AGND                | Analog ground. This pin should be electrically connected to GND close to the device                                                                                                                        |  |

| 6          | FB                  | Feedback pin. Inverting node of the transconductance error amplifier                                                                                                                                       |  |

| 7          | COMP                | Compensation pin. This pin is the output of the transconductance error amplifier and the input to the current comparator. Connect external compensation elements to this pin to stabilize the control loop |  |

| 8          | RT/CLK              | Resistor timing or external clock input pin                                                                                                                                                                |  |

| 9          | SS                  | Soft-start pin. An external capacitor connected to this pin sets the output voltage rise time. This pin can also be used for tracking                                                                      |  |

| 10,11,12   | SW                  | Internal power switch output pin. This pin is connected to the inductor and bootstrap capacitor                                                                                                            |  |

| 13         | BOOT                | Bootstrap pin. A bootstrap capacitor is connected between the BOOT pin and SW pin. The voltage across the bootstrap capacitor drives the internal high-side power MOSFET                                   |  |

| 14         | PGD                 | Power good indicator output. Asserts low if output voltage is low due to thermal shutdow over-current, over/under-voltage or EN shut down                                                                  |  |

| 15         | EN                  | Enable pin, internal pull-up current source. Pull below 1.2V to disable. Float to enable. Can be used to set the on/off threshold (adjust UVLO) with two additional resistors                              |  |

| EP         | Exposed Thermal Pad | Exposed Pad can be connected to GND, for best thermal performance thermal vias are recommended under the package                                                                                           |  |

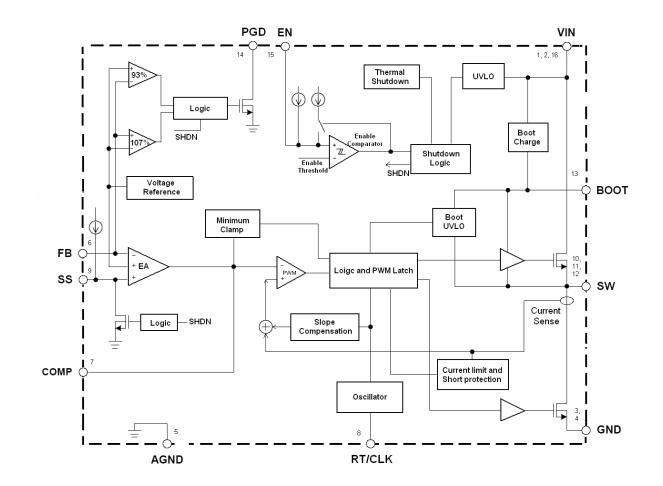

## **Functional Block Diagram**

## Absolute Maximum Ratings (Note 4)

| Symbol                                                | Parameter          | Rating                       | Unit |

|-------------------------------------------------------|--------------------|------------------------------|------|

| V <sub>IN</sub>                                       | VIN Pin Voltage    | -0.3 to 6.5                  | V    |

| V <sub>EN</sub>                                       | EN Pin Voltage     | -0.3 to 6.5                  | V    |

| V <sub>SW</sub>                                       | SW Pin Voltage     | -0.3 to V <sub>IN</sub> +0.3 | V    |

| V <sub>FB</sub>                                       | FB Pin Voltage     | -0.3 to 6.5                  | V    |

| V <sub>COMP</sub>                                     | COMP Pin Voltage   | -0.3 to 6.5                  | V    |

| V <sub>PGD</sub>                                      | PGD Pin Voltage    | -0.3 to 6.5                  | V    |

| V <sub>RT/CLK</sub> RT/CLK Pin Voltage                |                    | -0.3 to 6.5                  | V    |

| V <sub>SS</sub> SS Pin Voltage                        |                    | -0.3 to 6.5                  | V    |

| θ <sub>JA</sub> Thermal Resistance                    |                    | 70                           | °C/W |

| T <sub>J</sub> Operating Junction Temperature         |                    | -40 to +125                  | ℃    |

| T <sub>STG</sub> Storage Temperature                  |                    | -65 to +150                  | ٥C   |

| T <sub>LEAD</sub> Lead Temperature (Soldering, 10sec) |                    | +260                         | ℃    |

| _                                                     | ESD(Machine Model) | 200                          | V    |

| — ESD(Human Body Model)                               |                    | 2000                         | V    |

Note 4: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

## **Recommended Operating Conditions**

| Symbol                | Parameter                     | Min  | Мах | Unit |

|-----------------------|-------------------------------|------|-----|------|

| V <sub>IN</sub>       | Input Voltage                 | 2.95 | 5.5 | V    |

| I <sub>OUT(MAX)</sub> | Maximum Output Current        | 4    | _   | А    |

| T <sub>A</sub>        | Operating Ambient Temperature | -40  | +85 | ٥C   |

**Electrical Characteristics** ( $@V_{IN}=2.95$  to 5.5V, T<sub>A</sub>=+25°C, unless otherwise specified. Specifications with **boldface type** apply over full operating temperature range from -40 to +85°C.)

| Symbol                     | Parameters                                  | Conditions                                                                                  | Min  | Тур  | Мах  | Unit |  |

|----------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|------|--|

| SUPPLY VOLTA               | UPPLY VOLTAGE (VIN PIN)                     |                                                                                             |      |      |      |      |  |

| V <sub>IN</sub>            | Input Voltage                               | _                                                                                           | 2.95 | —    | 5.5  | V    |  |

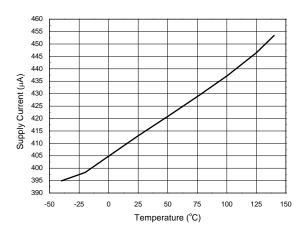

| IQ                         | Quiescent Current                           | V <sub>FB</sub> =0.9V, V <sub>IN</sub> =5V,<br>T <sub>A</sub> =+25°C, R <sub>T</sub> =400kΩ | _    | 360  | 575  | μA   |  |

| I <sub>SHDN</sub>          | Shutdown Supply Current                     | V <sub>EN</sub> =0V,T <sub>A</sub> =+25°C,<br>2.95V≤V <sub>IN</sub> ≤5.5V                   | _    | 2    | 5    | μA   |  |

| ENABLE AND U               | ENABLE AND UVLO (EN PIN)                    |                                                                                             |      |      |      |      |  |

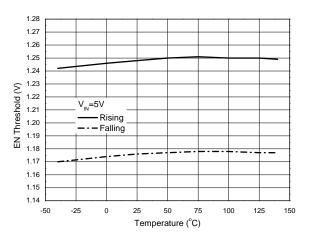

| $V_{\text{EN}_{\text{H}}}$ | Enable Threshold                            | Rising                                                                                      | 1.16 | 1.25 | 1.37 | V    |  |

| V <sub>EN_L</sub>          |                                             | Falling                                                                                     | —    | 1.18 | —    | V    |  |

| V <sub>UVLO</sub>          | Internal Under Voltage<br>Lockout Threshold | _                                                                                           | —    | 2.6  | 2.8  | V    |  |

| V <sub>HYS</sub>           | Internal Under Voltage<br>Hysteresis        | —                                                                                           | _    | 150  | —    | mV   |  |

**Electrical Characteristics** (Cont.) ( $@V_{IN}=2.95$  to 5.5V,  $T_A=+25^{\circ}C$ , unless otherwise specified. Specifications with **boldface type** apply over full operating temperature range from -40 to +85°C.)

| Symbol             | Parameters                              | Conditions                      | Min   | Тур   | Max   | Unit                |

|--------------------|-----------------------------------------|---------------------------------|-------|-------|-------|---------------------|

| VOLTAGE REFE       | ERENCE (FB PIN)                         | L                               |       |       |       |                     |

| V <sub>REF</sub>   | Voltage Reference                       | 2.95V≤V <sub>IN</sub> ≤5.5V     | 0.779 | 0.803 | 0.827 | V                   |

| MOSFET             |                                         |                                 | I     |       |       |                     |

| <u> </u>           | High Side Switch On-                    | V <sub>BOOT-SW</sub> =5V        |       | 30    | 60    | mΩ                  |

| R <sub>ON_H</sub>  | resistance                              | V <sub>BOOT-SW</sub> =2.95V     | —     | 44    | 70    | mΩ                  |

| D                  | Low Side Switch On-                     | V <sub>IN</sub> =5V             | —     | 30    | 60    | mΩ                  |

| R <sub>ON_L</sub>  | resistance                              | V <sub>IN</sub> =2.95V          | —     | 44    | 70    | mΩ                  |

| CURRENT LIMIT      | ſ                                       |                                 |       |       |       | ·                   |

| I <sub>LIMIT</sub> | Current Limit Threshold                 | _                               | 4.2   | 7.0   | _     | А                   |

| THERMAL SHU        | TDOWN                                   |                                 |       |       |       |                     |

| T <sub>TSD</sub>   | Thermal Shutdown                        | _                               | _     | 140   | _     | °C                  |

| _                  | Hysteresis                              | _                               | —     | 20    | _     | °C                  |

| TIMING RESIST      | OR AND EXTERNAL CLOCK (RT               | ſ/CLK PIN)                      |       |       |       | ·                   |

| _                  | Switching Frequency Range<br>(RT Mode)  | _                               | 200   | _     | 2000  | kHz                 |

| _                  | Switching Frequency Range<br>(CLK Mode) | _                               | 300   | _     | 2000  | kHz                 |

| f <sub>S</sub>     | Switching Frequency                     | R <sub>T</sub> =400kΩ           | 400   | 500   | 600   | kHz                 |

| —                  | Minimum CLK Pulse Width                 | _                               | 75    | —     | —     | ns                  |

| —                  | RT/CLK Voltage                          | R <sub>T</sub> =400kΩ           | —     | 0.5   | —     | V                   |

| _                  | RT/CLK High Threshold                   | _                               | —     | 1.6   | 2.2   | V                   |

| —                  | RT/CLK Low Threshold                    | _                               | 0.4   | 0.6   | —     | V                   |

| BOOT (BOOT P       | IN)                                     |                                 |       |       |       |                     |

| R <sub>BOOT</sub>  | BOOT Charge Resistor                    | V <sub>IN</sub> =5V             | —     | 16    | —     | Ω                   |

| —                  | BOOT-SW UVLO                            | V <sub>IN</sub> =2.95V          | —     | 2.2   | —     | V                   |

| SOFT START (S      | S PIN)                                  |                                 |       |       |       |                     |

| ISS                | Charge Current                          | V <sub>SS</sub> =0.4V           | —     | 2     | —     | μΑ                  |

| V <sub>SS</sub>    | SS to Reference Crossover               | 98% Nominal                     | —     | 1.1   | —     | V                   |

| POWER GOOD         | (PGD PIN)                               |                                 |       |       |       |                     |

|                    | Feedback Threshold                      | V <sub>FB</sub> Falling (Fault) | _     | 91    | _     |                     |

| V <sub>FB_TH</sub> |                                         | V <sub>FB</sub> Rising (Good)   | _     | 93    | _     | 0()(                |

|                    |                                         | V <sub>FB</sub> Rising (Fault)  | _     | 107   | _     | - %V <sub>REF</sub> |

|                    |                                         | V <sub>FB</sub> Falling (Good)  |       | 105   | _     |                     |

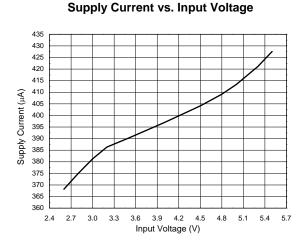

## **Performance Characteristics**

**UVLO Threshold vs. Temperature**

Efficiency vs. Output Current

Supply Current vs. Temperature

**EN Threshold vs. Temperature**

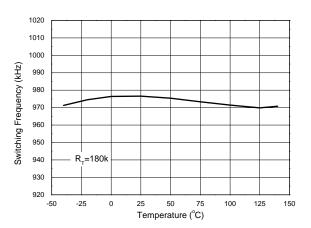

Switching Frequency vs. Temperature

## Performance Characteristics (Cont.)

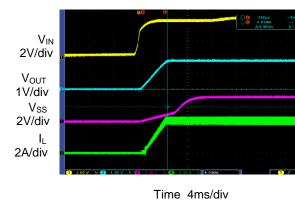

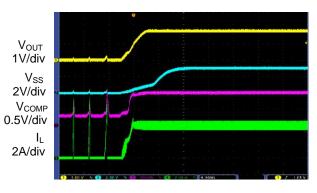

Start Up from VIN (VIN=5V, VOUT=1.8V, IOUT=4A)

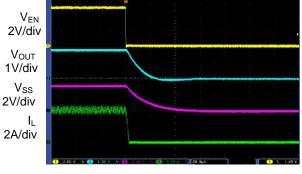

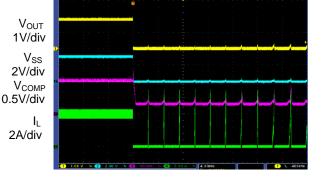

Disable IC (VIN=5V, VOUT=1.8V, IOUT=4A)

Time 20µs/div

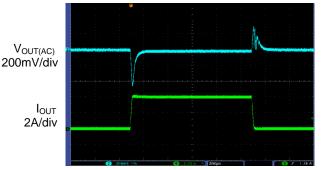

## Load Transient Response (V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.8V, I<sub>OUT</sub>=0 to 4A)

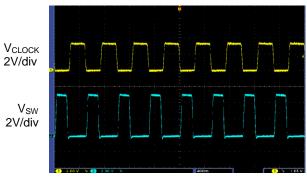

Synchronizing to External Clock (f<sub>CLOCK</sub>=2MHz)

Time 400ns/div

Time 4ms/div

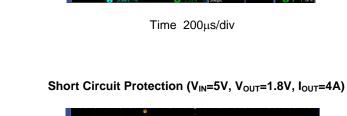

Short Circuit Recovery (VIN=5V, VOUT=1.8V, IOUT=4A)

Time 4ms/div

### **Application Note**

#### Theory of Operation

The AP3440 consists of a reference voltage module, slope compensation circuit, error amplifier, PWM comparator, current limit circuit, two Nchannel MOSFETs etc. (Refer to the Functional Block Diagram on page 3 for detailed information)

#### Soft-start

The AP3440 integrates an internal soft start circuit to minimize inrush currents or provide power supply sequencing during power up. A capacitor connected between SS pin and ground implements the soft-start time. The AP3440 has an internal pull-up current source of  $2\mu$ A, which charges the external slow start capacitor. Equation 1 calculates the required slow start capacitor, I<sub>SS</sub> is the internal slow start charging current of  $2\mu$ A, and V<sub>REF</sub> is the internal voltage reference of 0.803V.

$$C_{SS}(nF) = \frac{t_{SS}(mS) \times I_{SS}(\mu A)}{V_{REF}(V)} \qquad (1)$$

During normal operation, if the  $V_{IN}$  goes below the UVLO, or the EN pin is pulled below 1.2V, or a thermal shutdown occurs, the AP3440 will stop switching and the SS pin will be discharged to 40mV before reinitiating a powering up sequence.

#### Enable and Adjusting UVLO

The AP3440 are disabled when the  $V_{IN}$  falls below 2.6V. If an application requires a higher under-voltage lockout (UVLO), use the EN pin as shown in Figure 1 to adjust the input voltage UVLO by using two external resistors. The EN pin has an internal pull-up current source that provides the default condition of the AP3440 operating when the EN pin floats. Once the EN pin voltage exceeds 1.25V, an additional 2.55µA of hysteresis is added. When the EN pin is pulled below 1.18V, the 2.55µA hysteresis is removed. This additional current facilitates input voltage hysteresis.

For AP3440, the divider resistor R1 and R2 on the EN pin can be calculated according to equation 2 and 3.

$R2 = \frac{1.18 \times R1}{V_{stop} - 1.18 + R1 \times 3.2 \times 10^{-6}} \dots (3)$

Figure 1. Adjustable Under Voltage Lock Out

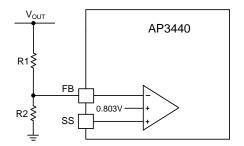

#### Adjusting Output Voltage

The output voltage is set with a resistor divider from the FB pin. It is recommended to use divider resistors with 1% tolerance or better. Start with a  $10k\Omega$  R2 resistor and use the equation 4 to calculate R1. To improve efficiency at very light loads consider using larger value resistors. If the values are too high, the regulator is more susceptible to noise and voltage errors from the FB input current are noticeable.

Resistor R1 can be calculated according to equation 4.

$R1 = R2 \times \left(\frac{V_{OUT}}{0.803} - 1\right)$  .....(4)

#### Synchronize Using the RT/CLK Pin

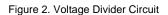

The RT/CLK pin of AP3440 is used to synchronize the converter with an external system clock referring to Figure 3. To implement the synchronization feature in a system, connect a square wave to the RT/CLK pin with an on-time of at least 75ns. When the clock is detected on the RT/CLK pin, a mode change occurs and the pin becomes a synchronization input. The internal amplifier is disabled. If clocking edges stop, the internal amplifier is re-enabled and the mode returns to the frequency set by the resistor. The low level of the square wave must be lower than 0.6V and the high level higher than 1.6V typically. The synchronization frequency range is from 300kHz to 2000kHz. The rising edge of the SW is synchronized to the falling edge of RT/CLK pin. Figure 4 shows a typical synchronizing waveform, the clock frequency is 2MHz.

Figure 4. Synchronizing Waveform

#### **Constant Switching Frequency and Timing Resistor**

The switching frequency of the AP3440 is adjustable over a wide range from 200kHz to 2000kHz by placing a resistor with maximum value of  $1000k\Omega$  and minimum of  $85k\Omega$ , respectively, on the RT/CLK pin. An internal amplifier holds this pin at a fixed voltage when connecting an external resistor to ground to set the switching frequency. The V<sub>RT/CLK</sub> is typically 0.5V. To determine the timing resistance for a given switching frequency, use the equation 5.

$$R_T(k\Omega) = \frac{311890}{f_{SW}(kHz)^{1.0793}}$$

....(5)

To reduce the solution size one should typically set the switching frequency as high as possible, but tradeoffs of the efficiency, maximum input voltage and minimum controllable on time should be considered.

PRODUCT

**≧**

#### **Over Current Protection**

The AP3440 implements a cycle-by-cycle current limit. The high side switch current is detected during each cycle. During SCP conditions,  $V_{OUT}$  is pulled down and  $V_{COMP}$  is drived to high, increasing the switch current. When the increased high side switch current is continuously detected to trigger the current limit of high side switch 6 times, the high side and low side switches are turned off for about 2.5ms. Then both switches start switching and they will not be turned off until the next 6 OCPs are triggered. The IC works with a hiccup mode during SCP conditions.

#### Power Good

The PGD pin output is an open drain MOSFET. The output is pulled low when the FB voltage enters the fault condition by falling below 91% or rising above 107% of the nominal internal reference voltage. There is a 2% hysteresis on the threshold voltage, so when the FB voltage rises to the good condition above 93% or falls below 105% of the internal voltage reference the PGD output MOSFET is turned off. It is recommended to use a pull-up resistor between the values of  $1k\Omega$  and  $100k\Omega$  to a voltage source that is 5V or less. The PGD is in a valid state once the VIN input voltage is greater than 1.2V.

#### Thermal Shutdown

The AP3440 implement an internal thermal shutdown to protect itself if the junction temperature exceeds +140°C. Switching is stopped when the junction temperature exceeds the thermal trip threshold. Once the die temperature decreases below +120°C, the device reinitiates the soft start operation. The thermal shutdown hysteresis is +20°C.

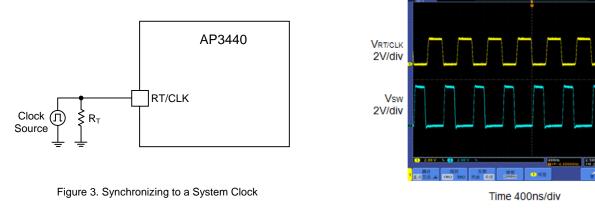

#### **Component Selection**

Typical application circuit of AP3440 is shown in Figure 5. For the major component selection please refer to the following section.

Figure 5. Typical Application of AP3440

#### Input Capacitor

The AP3440 requires a high quality ceramic, type X5R or X7R, input decoupling capacitor of at least 4.7µF effective capacitance and in some applications a bulk capacitor. The effective capacitance includes any DC bias effects. To ensure a stable operation, the input capacitor should be placed as close to the VIN pin as possible, and its value varies according to different load and different characteristic of input impedance.

There are two important parameters of the input capacitor: the voltage rating and RMS current rating. The voltage rating of the input capacitor should be at least 1.25 times larger than the maximum input voltage. The capacitor must also have a RMS current rating greater than the maximum input current ripple of the AP3440. The RMS current of input capacitor can be expressed as:

$$\mathbf{I}_{\text{CIN}_\text{RMS}} = \mathbf{I}_{\text{OUT}(\text{MAX})} \times \sqrt{\frac{\mathbf{V}_{\text{OUT}}}{\mathbf{V}_{\text{IN}}}} \times \left(1 - \frac{\mathbf{V}_{\text{OUT}}}{\mathbf{V}_{\text{IN}}}\right) \dots \dots \dots (7)$$

#### **Output Capacitor**

The output capacitor is the most critical component of a switching regulator. It is used for filtering output and keeping the loop stable. The typical value is 44µF.

The primary parameters for output capacitor are the voltage rating and the equivalent series resistance (ESR). A low ESR capacitor is preferred to keep the output voltage ripple low. The output ripple is calculated as the following:

$$\Delta V_{OUT} \approx \Delta I_L \times (R_{ESR} + \frac{1}{8 \times f \times C_{OUT}}) \dots (8)$$

Where f is the switching frequency,  $C_{OUT}$  is the output capacitance and  $\Delta I_L$  is the ripple current in the inductor.

#### Inductor

The inductor is used to supply smooth current to output when it is driven by a switching voltage. The higher the inductance, the lower the peak-topeak ripple current, as the higher inductance usually means the larger inductor size, so some trade-offs should be made when select an inductor. The AP3440 is a synchronous buck converter. It always works on continuous current mode (CCM), and the inductor value can be selected as the following:

$$L = V_{OUT} \times \left(\frac{V_{IN} - V_{OUT}}{f \times V_{IN} \times I_{OUT} \times k}\right) \dots (9)$$

Where  $V_{OUT}$  is the output voltage,  $V_{IN}$  is the input voltage,  $I_{OUT}$  is the output current, k is the coefficient of ripple current, and its typical value is 20% to 40%. Another important parameter for the inductor is the current rating. Exceeding an inductor's maximum current rating may cause the inductor to saturate and overheat. If inductor value has been selected, the peak inductor current can be calculated as the following:

It should be ensured that the current rating of the selected inductor is 1.5 times of the IPEAK.

#### **Slow Start Capacitor**

The slow start capacitor determines the output voltage soft start time during power up.

The slow start capacitor value can be calculated using equation 11.

In AP3440,  $I_{\text{SS}}$  is 2µA and  $V_{\text{REF}}$  is 0.803V.

#### **Bootstrap Capacitor**

A 0.1µF ceramic capacitor must be connected between the BOOT pin and the SW pin for normal operation. It is recommended to use a ceramic capacitor with X5R or better grade dielectric.

#### Feedback Resistors

It is recommended to use divider resistors with 1% tolerance or better. Start with a  $10k\Omega$  for the R7 resistor and use the equation 12 to calculate R6.

$$R6 = R7 \times \left(\frac{V_{OUT}}{0.803} - 1\right) \cdots (12)$$

AP3440 Document number: DS36691 Rev. 2 - 2

#### Compensation

The output capacitor and the load resistance largely determine where the error amplifier poles and zeros need to be placed for optimum transient response and loop stability. The corner frequency of the pole and zero generated by output capacitor are:

Where  $R_{LOAD}$  is the load resistance,  $C_{OUT}$  is the output capacitance and  $R_{ESR}$  is the capacitor ESR.

The error amplifier provides most of the loop gain. After selecting the output capacitor, the control loop is compensated by tailoring the frequency response of the error amplifier. The low frequency pole of the error amplifier is the dominant pole and is determined primarily by C<sub>COMP</sub> and the output resistance of the error amplifier as shown by:

Resistor R<sub>COMP</sub> adds a zero to the frequency response to control gain in the mid frequency range. This zero frequency is:

Where  $R_{COMP}$  and  $C_{COMP}$  are compensation resistor and capacitor connected to COMP pin,  $R_{OUT\_EA}$  is the output impedance of the error amplifier. A 7.5k $\Omega$  resistor and 2.7nF capacitor are used in typical application.

### Layout Consideration

PCB layout is very important to the performance of AP3440. The loop which switching current flows through should be kept as short as possible. The external components (especially  $C_{IN}$ ) should be placed as close to the IC as possible.

The feedback trace should be routed far away from the inductor and noisy power traces, and it needs to be routed as direct as possible. Locate the feedback divider resistor network near the feedback pin with short leads.

Since the SW connection is the switching node, the output inductor should be located very close to the SW pins, and the area of the PCB conductor is minimized to prevent excessive capacitive coupling.

The boot capacitor must also be located close to the device. The sensitive analog ground connections for the feedback voltage divider, compensation components, slow start capacitor and frequency set resistor should be connected to a separate analog ground trace.

The RT/CLK pin is sensitive to noise so the R<sub>T</sub> resistor should be located as close as possible to the IC and routed with minimal lengths of trace.

Figure 6. Top View of PCB Layout

Figure 7. Bottom View of PCB Layout

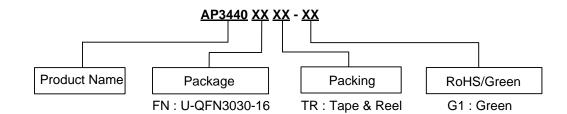

## **Ordering Information**

Diodes IC's Pb-free products with "G1" suffix in the part number, are RoHS compliant and green.

| Package      | Temperature Range | Part Number   | Marking ID | Packing          |

|--------------|-------------------|---------------|------------|------------------|

| U-QFN3030-16 | -40 to +85⁰C      | AP3440FNTR-G1 | B2D        | 5000/Tape & Reel |

## **Marking Information**

#

B2D: Marking ID (Per Datasheet) YWW: Year and Work Week of Mold Operation M: Assembly Site Code XX: The 7<sup>th</sup> & 8<sup>th</sup> Digits of Batch No. • Pin 1 Mark

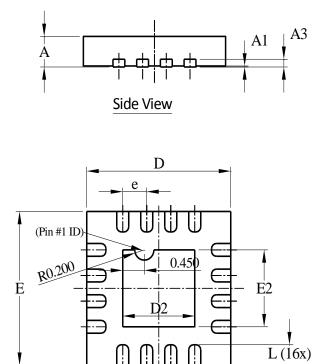

## **Package Outline Dimensions**

### (1) Package Type: U-QFN3030-16

| U-QFN3030-16         |      |      |       |  |  |

|----------------------|------|------|-------|--|--|

|                      | Туре | e B  |       |  |  |

| Dim                  | Min  | Max  | Тур   |  |  |

| Α                    | 0.55 | 0.65 | 0.60  |  |  |

| A1                   | 0    | 0.05 | 0.02  |  |  |

| A3                   | _    | _    | 0.15  |  |  |

| b                    | 0.18 | 0.28 | 0.23  |  |  |

| D                    | 2.95 | 3.05 | 3.00  |  |  |

| D2                   | 1.40 | 1.60 | 1.50  |  |  |

| E                    | 2.95 | 3.05 | 3.00  |  |  |

| E2                   | 1.40 | 1.60 | 1.50  |  |  |

| е                    | -    | _    | 0.50  |  |  |

| L                    | 0.35 | 0.45 | 0.40  |  |  |

| Z                    | -    | -    | 0.625 |  |  |

| All Dimensions in mm |      |      |       |  |  |

**Bottom View**

b (16x)

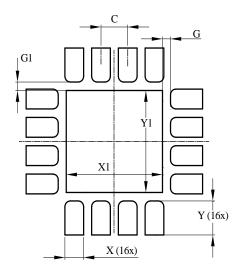

## **Suggested Pad Layout**

Z (8x)

(1) Package Type: U-QFN3030-16

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 0.500            |

| G          | 0.150            |

| G1         | 0.150            |

| Х          | 0.350            |

| X1         | 1.800            |

| Y          | 0.600            |

| Y1         | 1.800            |

|            |                  |

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2014, Diodes Incorporated

www.diodes.com